Challenges in the Chip Industry Low Yield and Tape-out Success Rate

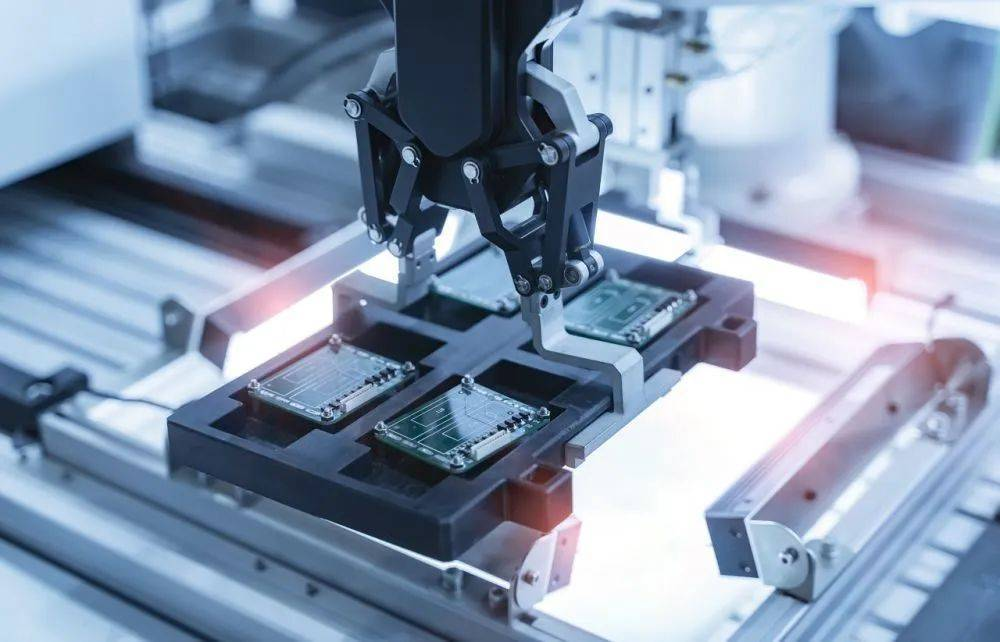

In today's digital age, chips, as the core of modern technology, have become a key driving force for economic and social development. From smartphones to supercomputers, from artificial intelligence to the Internet of Things, the performance and manufacturing level of chips directly affect the development and application of various technologies. However, despite the rapid progress of chip technology over the past few decades, the industry now faces two thorny problems: low manufacturing yield and low tape-out success rate. These issues are not only constraining the further development of the chip industry but also posing significant challenges to related companies.

Low Manufacturing Yield

The manufacturing yield of chips refers to the proportion of chips that meet quality standards out of the total production volume. In recent years, as chip manufacturing processes have continued to advance, the manufacturing yield has shown a downward trend. For example, Samsung's 3nm process is reported to have a yield of only about 20%, meaning that out of every 10 chips produced, 8 are unusable due to quality issues. This low yield situation has led many chip design companies, such as Qualcomm and Nvidia, to turn to TSMC for foundry services. Although TSMC is relatively advanced in yield control, it also faces the same challenges.

The following table shows some manufacturers' process nodes, yield levels, mass production times, and technical features:

Manufacturer | Process Node | Yield Level | Mass Production Time | Technical Features |

TSMC | Above 80% | Mass production | FinFET architecture | |

TSMC | Above 60% | End of 2025 | GAA nanosheet transistors | |

Samsung | 3nm (2nd Gen) | About 20% | Mass production | GAA architecture |

Samsung | 2nm | Above 40% | November 2025 (planned) | GAA architecture |

18A | 20-30% (controversial) | First half of 2025 tape-out | RibbonFET architecture |

The reasons for the low yield are multifaceted, mainly reflected in the following aspects:

1.Increased Process Complexity: As chip manufacturing processes advance from 10nm to 7nm, 5nm, 3nm, and beyond, each step poses higher demands on manufacturing equipment, technology, and materials. For example, the application of Extreme Ultraviolet Lithography (EUV) technology has driven progress in chip manufacturing, but its equipment is costly and requires extremely high operating environments and process precision. As process nodes shrink, the size of transistors approaches the atomic level, and even minor errors in the manufacturing process can lead to chip failure.

2.Material and Equipment Limitations: Advanced chip manufacturing requires high-purity silicon wafers, high-precision photoresists, and stable lithography machines. However, the supply and technical levels of these materials and equipment still face bottlenecks. For example, the global supply of EUV lithography machines is limited, and their operation requires an extremely high vacuum environment and stable light sources, which increase the difficulty and cost of manufacturing.

3.Cost and Market Competition: Chip manufacturing companies need to continuously invest huge amounts of money in research and development and equipment procurement in order to pursue more advanced processes. However, low yield leads to a significant increase in production costs, as companies have to allocate high R&D and manufacturing costs among the limited number of good products. This severely affects the economic benefits of chip manufacturing. At the same time, fierce market competition leads companies to rush products to the market before the technology is fully mature, further reducing the manufacturing yield.

Low Tape-out Success Rate

Tape-out refers to the process of transforming chip design into an actual product, involving a series of complex processes such as lithography, etching, and doping. According to data provided by Siemens, the first-time success rate of tape-out in the chip industry has continued to decline in recent years. In 2024, the first-time success rate was only 24%, and by 2025, this figure had further dropped to 14%. This means that out of 100 chip companies that perform tape-out, only 14 are likely to succeed, while the remaining 86 may fail. The significant drop in success rate poses huge pressure on the research and development and production of chip companies. The reasons for the plummeting tape-out success rate can be summarized as follows:

1.Increased Process Difficulty: Advanced chip manufacturing processes require higher precision and more complex procedures. For example, processes below 3nm require multiple exposure techniques and EUV lithography, and the complexity of these technologies significantly increases the probability of errors during tape-out.

2.Complex Chip Structures: Modern chips are becoming increasingly complex, with multiple architectures and types of chips integrated together. For example, System on Chip (SoC) integrates multiple functions such as processors, memory, and communication modules. This complexity greatly increases the difficulty of chip design and manufacturing, and even a slight mistake can lead to tape-out failure.

3.Accelerated Iteration Speed: To maintain competitiveness, chip companies need to speed up product iteration. In the past, the iteration cycle of chips was about 18 months on average, but now it has been shortened to less than 12 months. The compression of time makes it difficult for companies to fully verify and optimize during the design and manufacturing process, thereby reducing the tape-out success rate.

The Impact of the Dual Challenges on the Chip Industry

The simultaneous decline in chip yield and tape-out success rate is having a chain reaction on the entire semiconductor industry and the global tech economy. These two problems not only increase the manufacturing cost of chips but also extend the product launch cycle, ultimately leading to higher prices for end-user electronics and a slowdown in innovation. In the digital economy era, under the concept of "computing power equals economy," the difficulties of the chip industry have actually become a bottleneck for the development of the global tech economy. In response to this, companies in all aspects of chip manufacturing should take the following strategies:

The simultaneous decline in chip yield and tape-out success rate is having a chain reaction on the entire semiconductor industry and the global tech economy. These two problems not only increase the manufacturing cost of chips but also extend the product launch cycle, ultimately leading to higher prices for end-user electronics and a slowdown in innovation. In the digital economy era, under the concept of "computing power equals economy," the difficulties of the chip industry have actually become a bottleneck for the development of the global tech economy. In response to this, companies in all aspects of chip manufacturing should take the following strategies:

1.Technological Innovation and Breakthrough: Chip manufacturing companies need to increase R&D investment and explore new manufacturing processes and materials. For example, researching new semiconductor materials such as carbon nanotubes and two-dimensional materials to break through the physical limits of traditional silicon-based materials. At the same time, developing more advanced lithography, etching, and packaging technologies to improve manufacturing precision and efficiency.

2.Industry Chain Collaboration: Chip manufacturing is a complex system project that requires close cooperation among chip design companies, manufacturing companies, equipment suppliers, and material suppliers. By establishing industry alliances and cooperation mechanisms, all parties can share technical resources, optimize process flows, and jointly solve the problems of low manufacturing yield and low tape-out success rate.

3.Optimizing Design and Verification Processes: Chip design companies need to fully consider the limitations of manufacturing processes in the design stage and adopt advanced design tools and verification methods, such as virtual prototyping and simulation technology, to identify and solve potential problems in advance. At the same time, strengthen communication and collaboration with manufacturing companies to ensure seamless integration of design and manufacturing.

Conclusion

The development of the chip industry relies on continuous technological innovation and industry collaboration. Low manufacturing yield and low tape-out success rate are the two major challenges currently facing the chip industry, but they are also the driving forces for industry progress. By strengthening technology research and development, optimizing industry chain cooperation, and improving design and verification processes, the chip industry is expected to overcome these difficulties and achieve sustainable development. In the future, as technology continues to break through and applications expand, chips will play an important role in more fields and provide stronger support for the development of human society.

Conevo IC Distributor

Conevo is a leading distributor specializing in providing high-quality integrated circuits (ICs) to meet diverse industry needs. In briefly, Conevo Electronics offers a comprehensive one-stop solution for sourcing high-quality IC components.

● TPS54335ADRCR: A high-efficiency synchronous step-down converter with an input voltage range of 3V to 36V, capable of delivering up to 3.3A output current. It features integrated MOSFETs and a compact package size, making it ideal for space-constrained designs.

● AD633ARZ: A precision analog multiplier/divider IC with a wide bandwidth and low distortion. It supports four-quadrant operation and is suitable for applications requiring high-precision signal processing, such as modulators, demodulators, and variable gain amplifiers.

● DRV8701PRGER: A high-side gate driver with built-in charge pump, designed for driving N-channel MOSFETs in various motor control and power management applications. It offers high reliability and ease of use with minimal external components required.

Website: www.conevoelec.com

Email: info@conevoelec.com