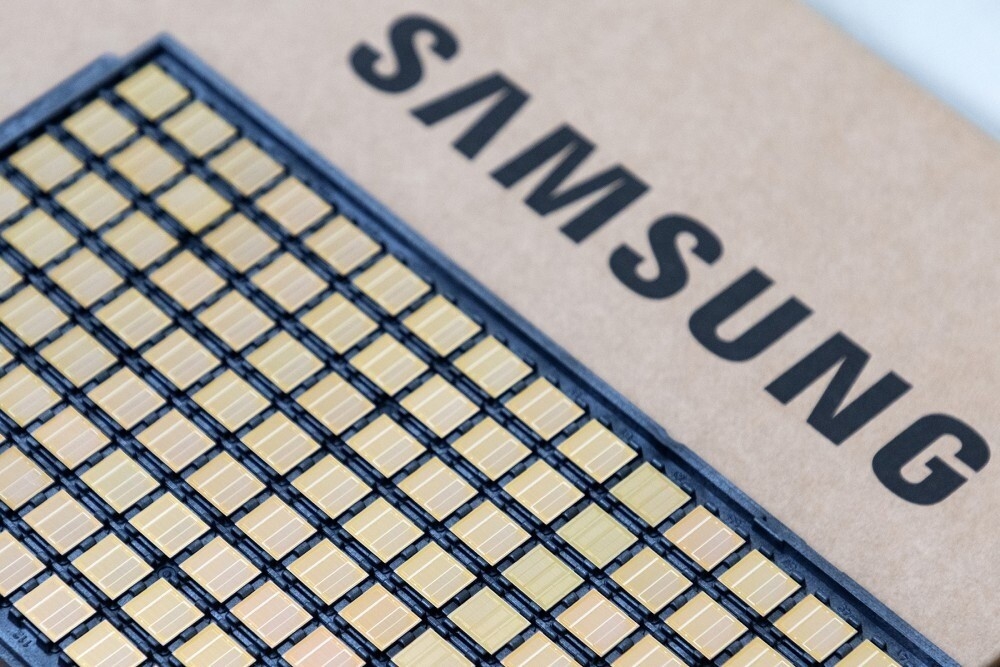

Samsung Electronics Halts 2D NAND Production at Hwaseong Line 12

Samsung Electronics is accelerating its strategic transformation in the memory chip business. The company will officially cease 2D NAND flash production at its Hwaseong Campus Line 12 as early as March 2026. With a monthly capacity of 80,000 to 100,000 12-inch wafers, the production line will be fully converted to back-end manufacturing of 1c nanometer-class DRAM to address the explosive demand for high-bandwidth memory in the artificial intelligence era.

Inevitable Evolution of Memory Technology

The phase-out of 2D NAND flash represents the inevitable outcome of storage technology evolution. Since Samsung pioneered the mass production of 1Gb NAND flash globally in 2002, planar architecture had propelled the company to the pinnacle of global flash memory manufacturing. However, with the commercialization of 3D V-NAND technology in 2013, vertical stacking architecture—with its superior storage density, reliability, and performance—gradually displaced traditional planar structures. Although Samsung maintained limited 2D capacity to serve niche markets such as USB drives after the 3D era commenced, market demand for 2D products has dwindled to negligible levels as 3D NAND costs continued to decline.

This production halt comes 24 years after Samsung initiated 2D NAND manufacturing and 13 years following the mass production of 3D NAND, marking the storage industry's complete transition from planar to three-dimensional technology paradigms. Major competitors including Micron and SK Hynix have already completed their transitions to all-3D product portfolios between 2020 and 2022.

Strategic Rationale for Capacity Restructuring

The transformation of Hwaseong Line 12 represents not a simple shutdown but a pivotal move in Samsung's "legacy-to-advanced process conversion" strategy. The revamped line will function as a DRAM back-end production base, specializing in critical back-end processes including metallization and surface treatment, creating synergies with front-end lines within the campus. This division of labor is expected to significantly enhance overall DRAM production efficiency at the Hwaseong facility while alleviating current capacity bottlenecks for 1c nanometer DRAM.

The transformation of Hwaseong Line 12 represents not a simple shutdown but a pivotal move in Samsung's "legacy-to-advanced process conversion" strategy. The revamped line will function as a DRAM back-end production base, specializing in critical back-end processes including metallization and surface treatment, creating synergies with front-end lines within the campus. This division of labor is expected to significantly enhance overall DRAM production efficiency at the Hwaseong facility while alleviating current capacity bottlenecks for 1c nanometer DRAM.

The 1c nanometer process constitutes Samsung's sixth-generation 10nm-class DRAM technology and serves as the fundamental building block for its HBM4 high-bandwidth memory. As AI server demand surges, HBM has become a strategically scarce resource. Samsung commenced HBM4 shipments in February 2026, utilizing 1c DRAM die stacking combined with 4nm logic base dies to achieve data transfer speeds of 11.7 Gbps—substantially exceeding JEDEC standards. Samsung's HBM business revenue is projected to double in 2026.

Global Capacity Realignment

Capacity adjustments at the Hwaseong facility are triggering a comprehensive restructuring of Samsung's global manufacturing footprint. Reduced NAND capacity in Korea will be offset by the Xi'an facility, which currently accounts for approximately 40 percent of Samsung's NAND output and is upgrading from 128-layer products to advanced processes exceeding 200 layers. Concurrently, the Pyeongtaek Campus P4 fab has transitioned from its original mixed-production model encompassing DRAM, NAND, and foundry operations to a dedicated DRAM manufacturing base.

These adjustments demonstrate Samsung's clear strategic focus: the Hwaseong facility will concentrate resources on DRAM production, particularly 1c nanometer high-end products for the AI era. The Pyeongtaek fab will continue to handle both DRAM and NAND, while the Xi'an facility will undertake large-scale NAND capacity expansion. Industry forecasts indicate that Samsung's 1c DRAM monthly capacity will reach 200,000 wafers in the second half of 2026, with the Line 12 conversion contributing significant incremental volume.

CONEVO -- Semiconductor Distribution Partner

As a globally recognized independent distributor, CONEVO specializes in bridging supply gaps for critical semiconductor components across industrial automation, automotive systems, AI infrastructure, and consumer electronics sectors. CONEVO maintains strategic inventory spanning high-performance FPGAs, precision power management ICs, automotive-grade microcontrollers, and advanced interface solutions, ensuring rapid response to urgent procurement needs. CONEVO's Featured IC Recommendations:

● DS28EC20P+T: A 20Kb 1-Wire EEPROM from Maxim Integrated featuring built-in SHA-256 authentication engine and unique 64-bit ROM ID.

● SN74HC373NSR: Texas Instruments' octal transparent D-type latch with 3-state outputs, delivering high-speed CMOS performance for temporary data storage.

● 5SGXMA3K2F35C2N: Intel/Altera's Stratix V GX FPGA offering 340K logic elements, 12.5Gbps transceivers, and hardened PCI Express Gen3 x8 cores.

Website: www.conevoelec.com

Email: info@conevoelec.com