Japanese Government Approves Additional ¥631.5 Billion Subsidy for Rapidus

On April 11, 2026, Japan's Ministry of Economy, Trade and Industry (METI) formally announced that it has approved an additional ¥631.5 billion (approximately $4 billion) in financial support for Rapidus, a semiconductor foundry startup. The funding aims to accelerate the company's entry into the fiercely competitive advanced AI chip manufacturing sector and reduce Japan's industrial dependence on Taiwan Semiconductor Manufacturing TSMC.

The Japanese government projects that its cumulative investment in Rapidus will reach ¥2.6 trillion (approximately $16.3 billion) by March 2027. An external committee established by METI has completed an on-site inspection of Rapidus's Hokkaido wafer fab and has officially recognized the company's technological progress.

Latest Funding Allocation

According to reports, the additional funding will be directly allocated to support Rapidus in the research, development, and foundry production of chips for IT giant Fujitsu. Fujitsu plans to develop NPU chiplets for AI inference applications based on Rapidus's 1.4nm process node, and integrate them with its self-developed Arm-based Monaka CPU within a single package for deployment in Japan's next-generation supercomputer "Fugaku NEXT" and data center systems.

According to reports, the additional funding will be directly allocated to support Rapidus in the research, development, and foundry production of chips for IT giant Fujitsu. Fujitsu plans to develop NPU chiplets for AI inference applications based on Rapidus's 1.4nm process node, and integrate them with its self-developed Arm-based Monaka CPU within a single package for deployment in Japan's next-generation supercomputer "Fugaku NEXT" and data center systems.

The Fujitsu project carries a development cost of approximately ¥58 billion, with roughly two-thirds subsidized by Japan's New Energy and Industrial Technology Development Organization (NEDO). Beyond Fujitsu, Rapidus has also secured orders for Canon's image processing chips and AI chips co-developed by IBM and Tenstorrent, gradually expanding its customer portfolio.

2nm Mass Production Progress

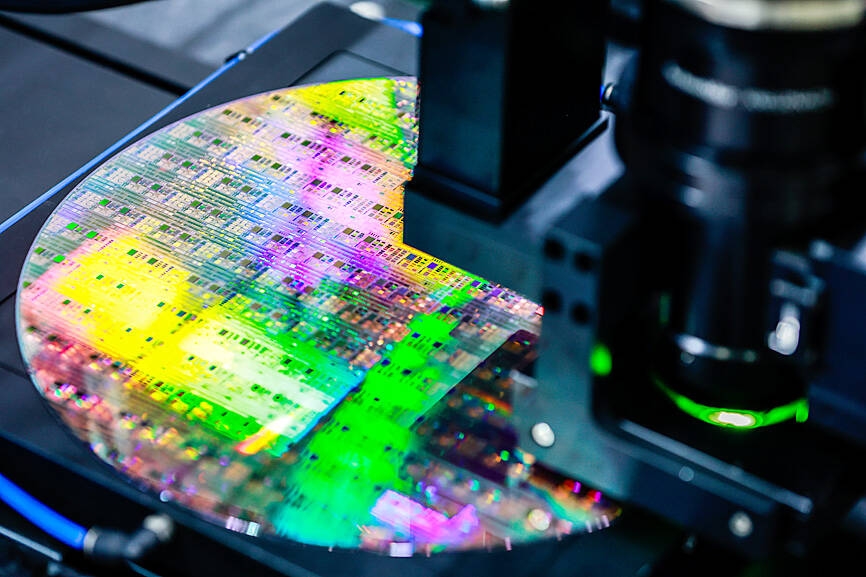

On the technological front, Rapidus launched its pilot production line in April 2025 and completed tape-out of 2nm GAA test chips in August of the same year. The company plans to deliver 2nm Process Design Kits (PDK) to customers in the first quarter of 2026. Its "2HP" process achieves a logic density of 237.31 MTr/mm², essentially on par with TSMC's N2 process.

Rapidus plans to commence mass production of 2nm chips in the second half of fiscal year 2027, with an initial monthly capacity of 6,000 wafers, targeting an increase to 25,000 wafers per month within approximately one year of mass production ramp-up. For the 1.4nm node bridging 2nm and 1nm, Rapidus aims to achieve mass production by 2029.

Supporting Facilities Commissioned

Rapidus has already commissioned an Analysis Center and an Advanced Packaging Facility (RCS) in Chitose, Hokkaido. Both facilities serve as supporting infrastructure for its 2nm wafer fab, IIM-1.

The Analysis Center is equipped with cutting-edge electron microscopes capable of physical analysis, environmental and chemical analysis, electrical characterization, and reliability testing—enabling real-time closed-loop verification between manufacturing and analysis. Located at Seiko Epson's Chitose facility, the RCS has already begun small-scale trial production of 600mm×600mm RDL interposers and other products. Utilizing glass substrate technology, it can enhance AI chip production efficiency by more than tenfold. Additionally, a development center specializing in back-end processes (packaging and testing) has also commenced operations.

CONEVO Chips Distributor

CONEVO is an independent distributor of electronic components, specializing in providing high-performance IC solutions for aerospace, automotive electronics, industrial control, medical equipment, and consumer electronics. Conevo mainly offers core products such as FPGA, MCU, DSP, ADC/DAC converters, MLCC, and power management chips. It can also provide one-stop services from chip selection, BOM optimization to PCB design support, ensuring that customers receive high-quality genuine components and guaranteed fast delivery. The selected IC models today are as follows:

● IS46QR81024A-083TBLA2: A high-speed low-power DDR3L SDRAM memory chip designed for high-density data processing applications, providing stable and reliable memory performance.

● TCA9534APWR: A low-power 8-bit I²C bus GPIO expander launched by TI, featuring interrupt output and configuration register functions, suitable for portable devices and sensor interface expansion.

● MP2451DT-LF-Z: An efficient synchronous buck converter manufactured by MPS, supporting a wide input voltage range and light-load high-efficiency mode, being an ideal power management solution for battery-powered systems.

● 88E1512PB2-NNP2I000: A Marvell single-port Gigabit Ethernet PHY transceiver, integrating energy-saving Ethernet functions, providing high-reliability connections for industrial networks and communication equipment.

Website: www.conevoelec.com

Email: info@conevoelec.com